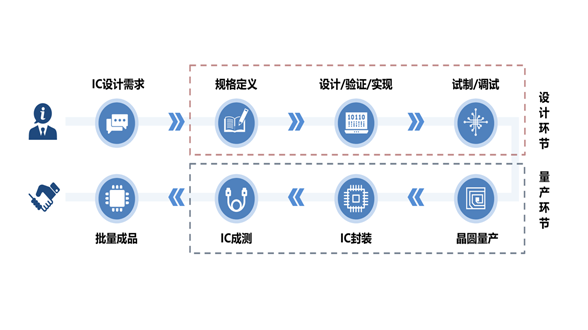

根据客户需求或设计规格书,综合运用基于EDA软件的应用级开发、纳米级工艺定制版图设计、基于FPGA的IP和集成电路产品验证、高适应性通用基础IP等自主研发形成的核心技术,进行电路设计和验证、版图设计和验证;通过现有技术检索及筛查、风险审核及控制等手段,防范设计成果侵权;最终完成流片、封装及测试等环节,并将成品交付客户。

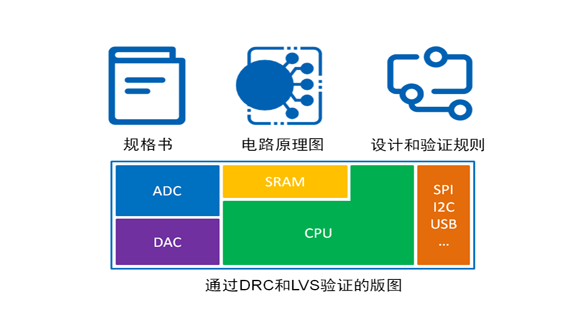

根据客户提供的技术规格书,电路原理图,版图设计和验证规则,完成定制版图的设计和验证。

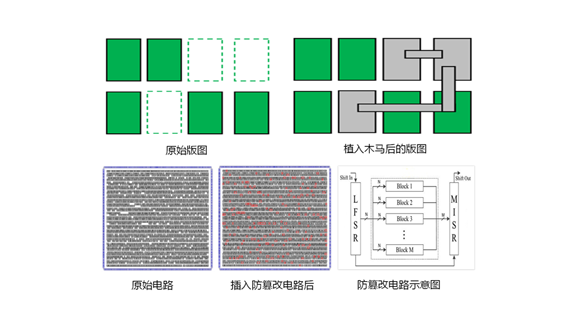

版图数据中完成布局布线后会总会留有一定的单元空白区。一般情况下这些空白区域都会被设计者用dummy单元进行填充,这些dummy单元和其他空白的走线区域极有可能被利用进行木马植入或者FIB物理攻击。

安全优化设计将为版图加入一个防篡改识别电路,用于检测是否版图中被植入了木马。一旦版图被篡改并植入了木马,则防篡改电路会立刻发现变化。

不同于简单的dummy单元的填充,安全优化设计会将单元空白区域用有逻辑意义的单元进行填充,并将这些填充单元利用空白走线区域进行连接形成若干个有具体逻辑意义的防篡改电路。如果芯片中被植入了木马,那么必定防篡改电路的功能会发生变化,通过芯片流片后的安全测试就能检测出来。对于防篡改电路的加固是在原有设计版图完成的情况下进行,因此不会对原有设计产生干扰。

此外,利用安全加固EDA软件,通过在芯片的顶层进行有源金属屏蔽层的生成,可以有效的对抗FIB修改的侵入方式。

根据客户提供的设计要求,综合运用IC安全可信设计、基于EDA软件的应用级开发、基于FPGA的IP和集成电路产品验证等自主研发形成的核心技术,进行电路和版图的可靠性加固设计和验证,并最终交付设计验证完成的电路、版图和验证过程数据。